MK米客方德SD NAND参考设计软件开发

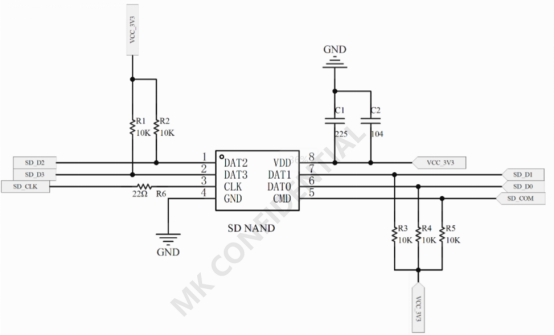

1、 参考电路:

R1~R5 (10K-100 kΩ)是上拉电阻,软件开发当SD NAND处于高阻抗模式时,保护CMD和DAT线免受总线浮动。

即使主机使用SD NAND SD模式下的1位模式,主机也应通过上拉电阻上拉所有的DATO-3线。

R6(RCLK)参考0-120 Ω。

2、电源VDD(VCC_3V3)建议单独供电,且需要注意提供SD NAND电流供电能力不小于200mA。

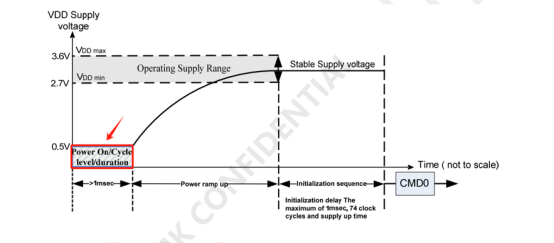

3、下图是SD协议规定的上电规范,SD NAND的工作电压范围是2.7V-3.6V:

为了确保芯片能正常上电初始化,电压要在0.5V以下至少1ms;软件开发电源上升的时候需要保持电源是稳定的、持续上升的,上升到正常工作电压的时间是0.1ms-35ms;主机关闭电源时,将卡的VDD降至0.5伏以下的最小周期为1ms。在断电期间,DAT, CMD和CLK应断开连接或由主机驱动到逻辑0,以避免工作电流通过信号线引出的情况。

二、Layout 设计说明

1、数据线应尽量保持等长,以减少时序偏差和提高信号的同步性。

2、对于CLK时钟线,尽可能进行包地处理。对于走线阻抗,控制阻抗50欧姆。

3、SD NAND芯片最好靠近主控芯片放置,以减少走线长度和干扰。

4、LGA 9*12.5 封装焊盘分两侧 2*8分布,其中同名网络 layout 时可以连接在一起,方便后续更换物料时兼容 LGA6.0×8mm,LGA6.6×8.0mm封装(如下图)。

芯片解密

芯片解密